|

MCU

|

STM32F103(ST)

|

|

목표

|

Crystal의 적절한 Load capacitance 선정

|

Crystal Load Capacitance?

- MCU를 포함한 전자 회로 설계시 Crystal을 뺄수 없다. 내장 발진기도 있으나 정밀도를 위해 외부 발진기를 다는데, 이때 옆에 붙이는 Capacitor가 Load Capacitor.

- 적당히, 다른 사람 회로도를 보고 Capacitor 붙이지 말고 아래 선정 방법을 참고

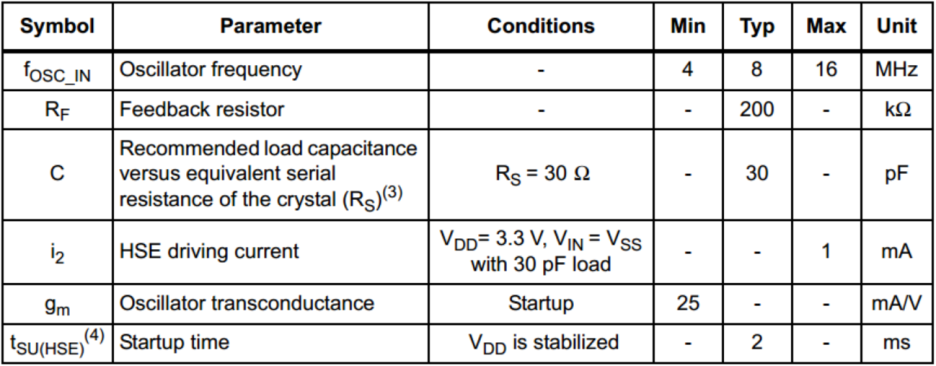

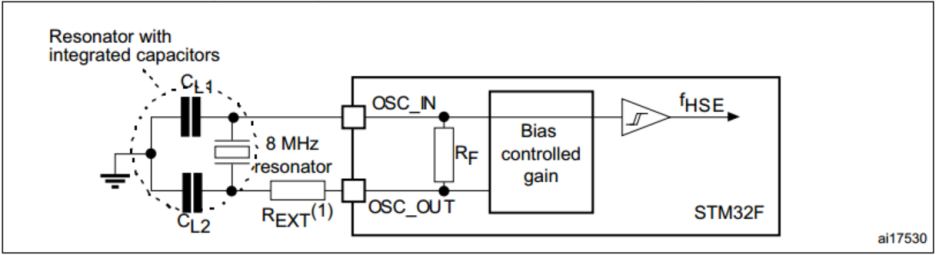

아래 사진은 STM32F103VCT의 datasheet

Load Capacitance 공식

|

CL = CL1 x CL2 / (CL1 + CL2) + Cstray

|

CL : Load Capacitance of Crystal

CL1 : X1 Input Capacitance(우리가 알아내야 하는 값)

CL2 : X2 Input "

Cstray : 핀 캐패시턴스 및 보드 또는 트레이스 PCB 관련 캐패시턴스

CL1 = CL2 라고 가정하면,

CL = CL1 x CL1 / (CL1 + CL1) + Cstray

CL = CL1^2 / 2CL1 + Cstray

CL = CL1 / 2 + Cstray

CL - Cstray = CL1 / 2

2(CL - Cstray) = CL1

|

CL1 = 2(CL - Cstray)

|

예를 들어 Load Capacitance를 구해 보자.

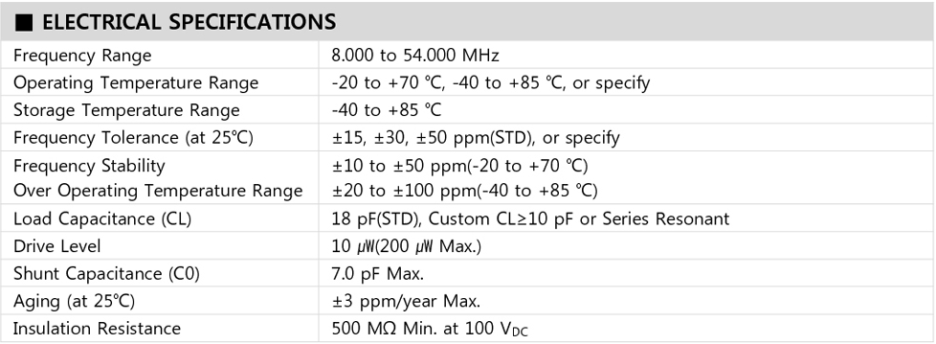

다음의 Crystal을 사용할 때 Load Capacitance는?

CL = 18pF(보통 5 ~ 25 pF)

Cstray = 5pF으로 가정

(PCB 설계가 간단하고 트레이스가 짧다면 3pF로 가정, 트레이스가 길거나 복잡하다면 4~5pF로 가정)

CL1 = 2(CL - Cstray)

CL1 = 2(18 - 5)

CL1 = 26pF

CL1 = CL2 =26pF

LSE의 Load capacitor 구하는 방법은 똑같으나, Crystal의 Load capacitance 값이 다르고, 허용 Load capacitance 값이 다르므로 datasheet를 읽어 볼 것.

'전자 회로 설계 > 회로 및 제어' 카테고리의 다른 글

| 전자 회로 설계 - 시리얼 통신(RS-232) (0) | 2025.03.16 |

|---|---|

| PSpice for TI - Simulation(Transistor) (0) | 2025.03.16 |

| 전자 회로 설계 - Relay, SSR 사용과 회로 설계 (0) | 2025.03.16 |

| 전자 회로 설계 - [I/O] PUSH-PULL, OPEN-DRAIN (0) | 2025.03.16 |

| 전자 회로 설계 - Flyback(Freewheeling) diode, 환류 다이오드 (0) | 2025.03.16 |