USB PHY?

- USB PHY(Physical Layer)는 USB 통신의 물리 계층을 담당하는 하드웨어 모듈

- USB 프로토콜에 따라 데이터를 전송하거나 수신할 때, 디지털 신호와 아날로그 신호 간의 변환

- USB 디바이스 또는 호스트가 실제로 데이터 전송을 가능하게 함

1. USB PHY의 역할

1-1. 디지털-아날로그 변환 (DAC)

- 디지털 신호를 아날로그 전압 또는 전류로 변환해 USB 라인(D+/D-)으로 출력

1-2.아날로그-디지털 변환 (ADC)

- USB 라인에서 수신한 신호(D+/D-)를 디지털 신호로 변환해 USB 컨트롤러로 전달

1-3. 신호 레벨 조정

- USB 표준(USB 2.0, 3.0 등)에 맞는 전압 및 전류 수준을 유지

- 고속 신호 전송(USB 2.0의 480 Mbps, USB 3.0의 5 Gbps 등)을 지원

1-4. USB 프로토콜 구현 보조

- 신호 인코딩 및 디코딩 (NRZI, 8b/10b 등)

- 동기화 및 클럭 복구

- 디바이스 연결 상태(attach/detach)와 같은 이벤트 감지

1-5. 전력 관리

- USB 라인의 전력 신호(VBUS)를 감지

- 저전력 및 유휴 상태 관리

2. USB PHY의 구성 요소

2-1. 트랜시버

- USB 라인(D+, D-)으로 신호를 송수신

- FS (Full Speed), HS (High Speed), SS (Super Speed)와 같은 USB 데이터 전송 속도를 지원

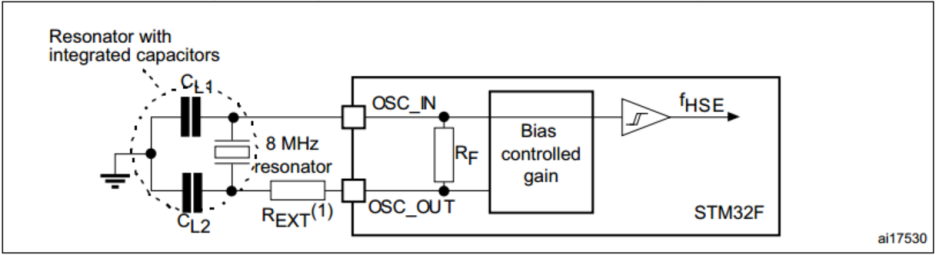

2-2. 클럭 생성기

- 데이터 전송의 동기화를 위해 안정적인 클럭 신호를 생성

2-3. 전력 감지 회로

- USB 디바이스가 VBUS 신호를 통해 연결 상태를 인식

2-4. 차동 증폭기

- USB의 차동 신호(D+/D-)를 증폭하여 신호 왜곡을 최소화

2-5. ESD 보호 회로

- USB 포트에서 발생할 수 있는 정전기 방전을 방지

3. USB PHY의 종류

3-1. USB 1.1/2.0 PHY

- Full Speed(12 Mbps)와 High Speed(480 Mbps)를 지원

- 트랜시버가 D+/D- 라인에서 NRZI 인코딩과 디코딩 수행

- 저전력 설계가 강조됨

3-2. USB 3.0 PHY

- Super Speed(5 Gbps)를 지원

- 고속 데이터 전송을 위해 8b/10b 인코딩 사용

- 기존 USB 2.0 PHY와 병렬로 동작

3-3. USB Type-C PHY

- 양방향(리버서블) 연결 지원

- USB PD(Power Delivery)와 호환 가능

- 데이터 및 전력 전송을 동시에 처리

4. USB PHY의 통합 방식

4-1. Discrete USB PHY

- 독립된 칩 형태로 제공

- 특정 USB 컨트롤러와 결합해 사용

- 유연성은 높지만 설계 복잡성이 증가

4-2. Integrated USB PHY

- MCU나 SoC에 내장되어 제공

- 간단한 설계와 공간 절약 가능

- 저비용 소형 디바이스에 적합

5. 추천 USB PHY IC

5-1. Microchip - USB3300

- USB 2.0 HS PHY

- ULPI 인터페이스 제공

- 저전력 및 고성능 설계

5-2. Texas Instruments - TUSB1210

- USB 2.0 PHY

- ULPI 인터페이스

- 고속 신호 전송과 간단한 설계 지원

5-3. Synopsys - DesignWare PHY

- USB 3.0/3.1 PHY IP

- SoC 설계에 적합

5-4. Cadence - USB PHY IP

- 고속 및 전력 효율적 USB PHY 솔루션

6. USB PHY를 사용할 때 고려 사항

6-1. 지원하는 USB 표준

- USB 2.0, USB 3.0, USB Type-C 등 요구 사항에 맞게 선택

6-2. 호환성

- 사용하려는 MCU나 SoC와 인터페이스 호환성 확인 (ULPI, PIPE 등)

- USB 2.0, USB 3.0, USB Type-C 등 요구 사항에 맞게 선택

6-3. 전력 소비

- 저전력 설계가 필요한 경우 ESD 보호와 전력 관리 기능 포함 여부 확인

6-4. 설계 복잡도

- 외부 USB PHY가 필요한지, 아니면 통합된 PHY를 사용할지 결정

'전자 회로 설계 > 회로 및 제어' 카테고리의 다른 글

| 전자 회로 설계 - 시리얼 통신(TCP/IP) (0) | 2025.03.16 |

|---|---|

| 전자 회로 설계 - 시리얼 통신(RS-232) (0) | 2025.03.16 |

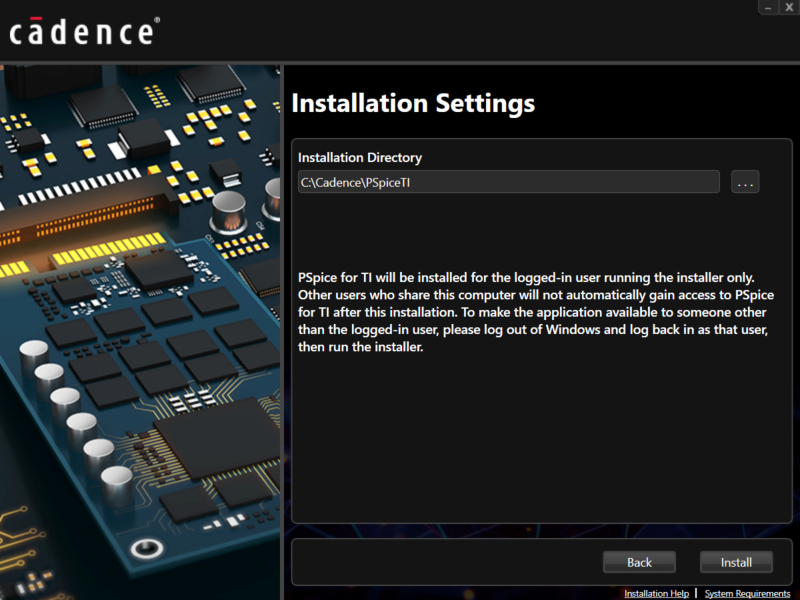

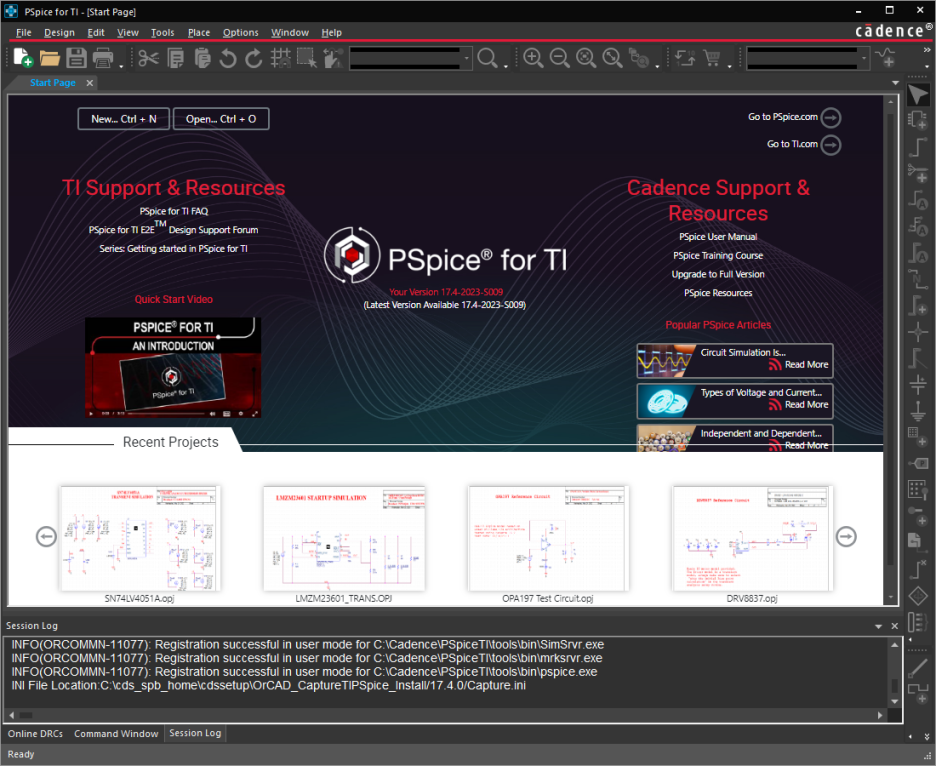

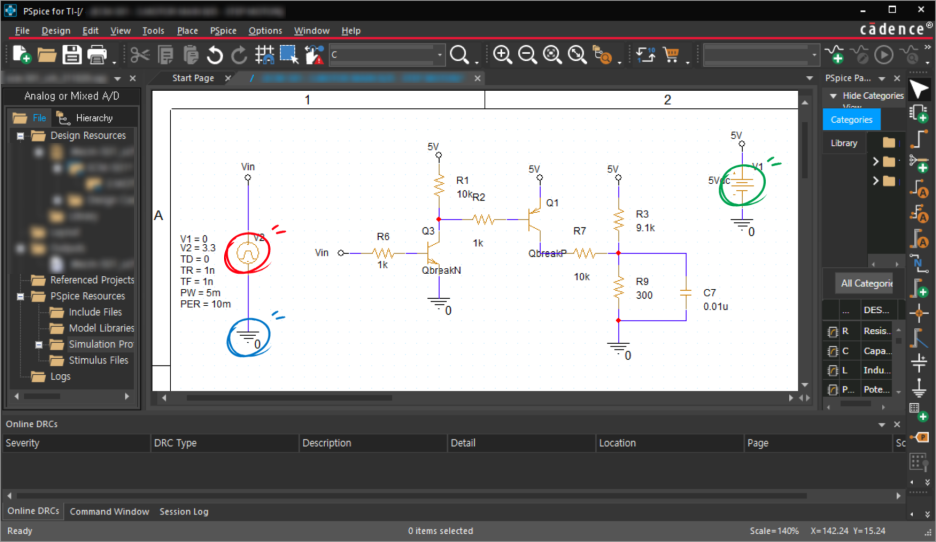

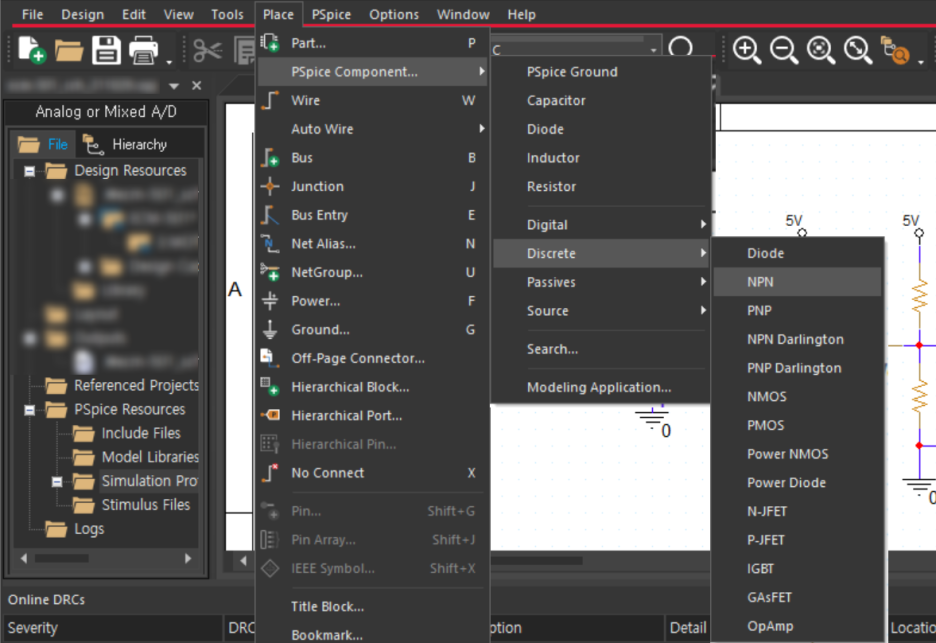

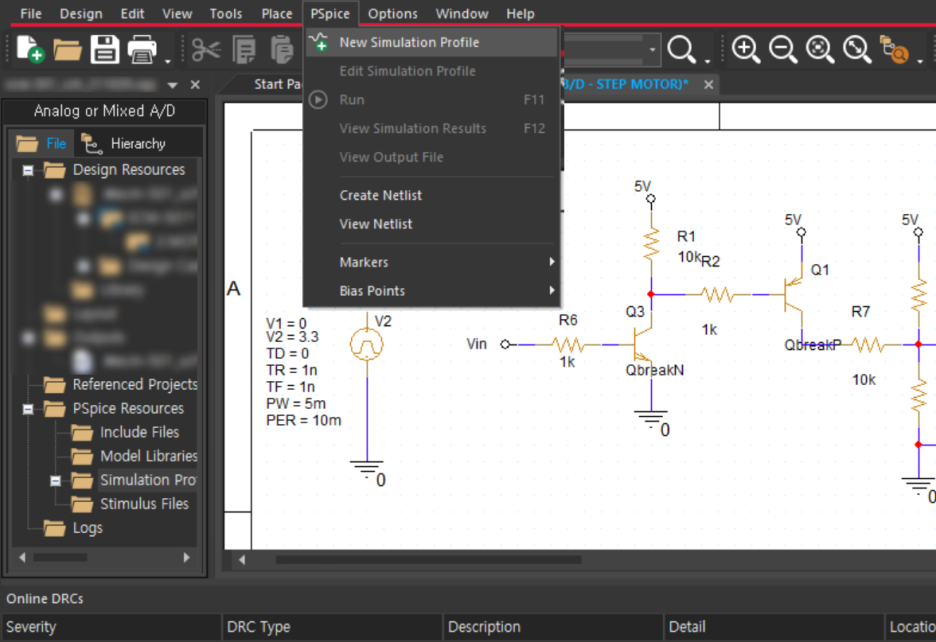

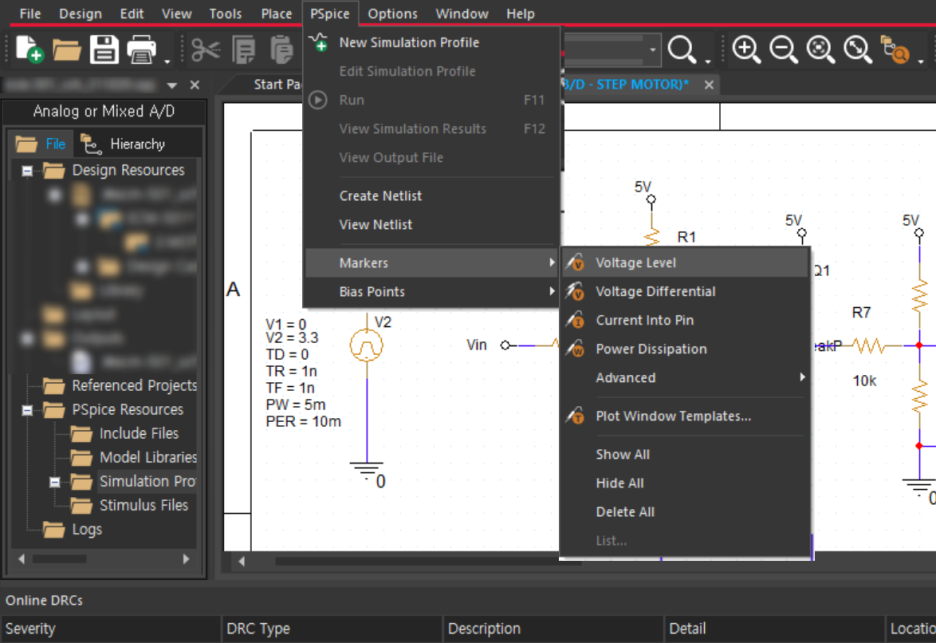

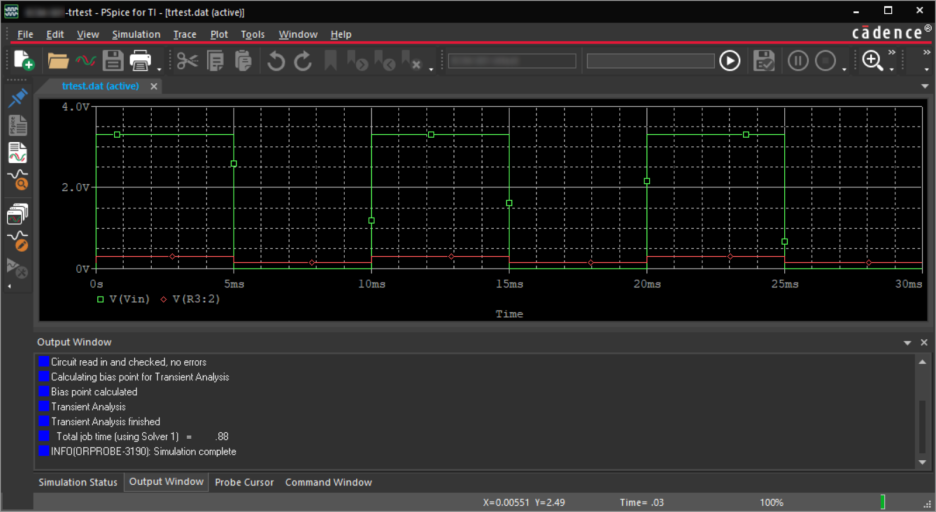

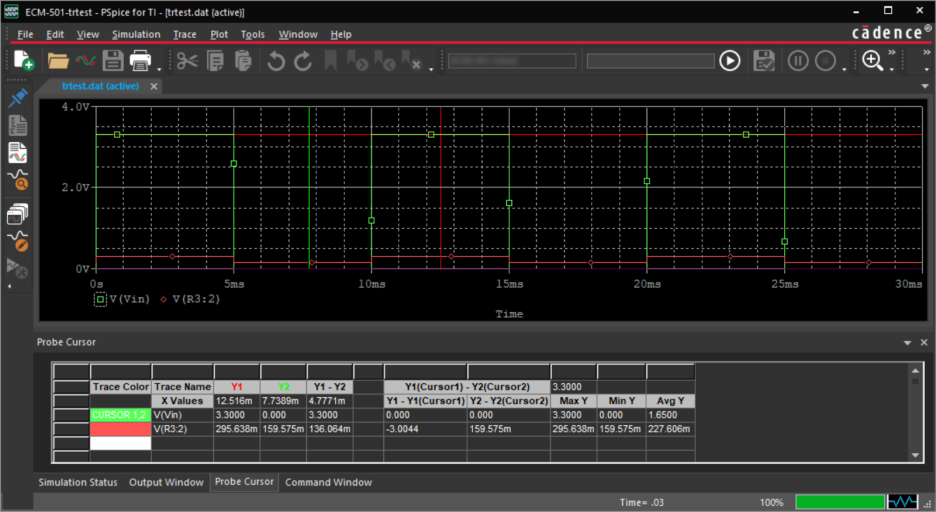

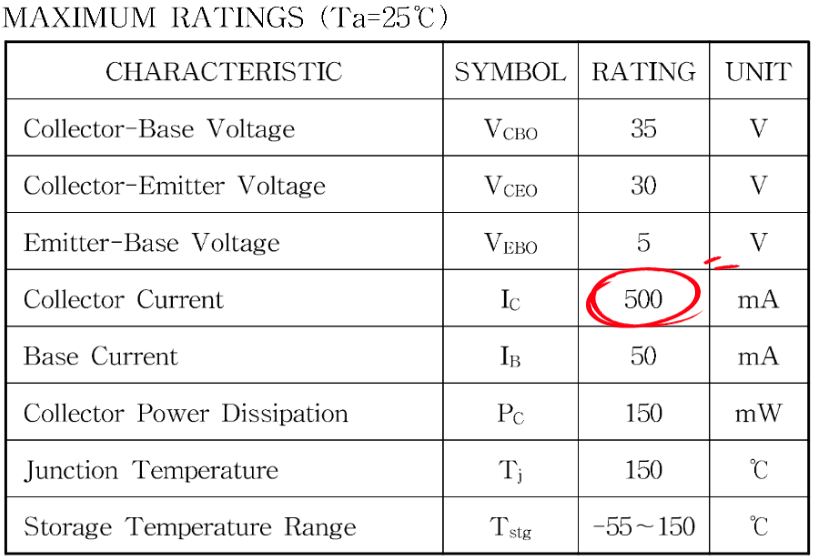

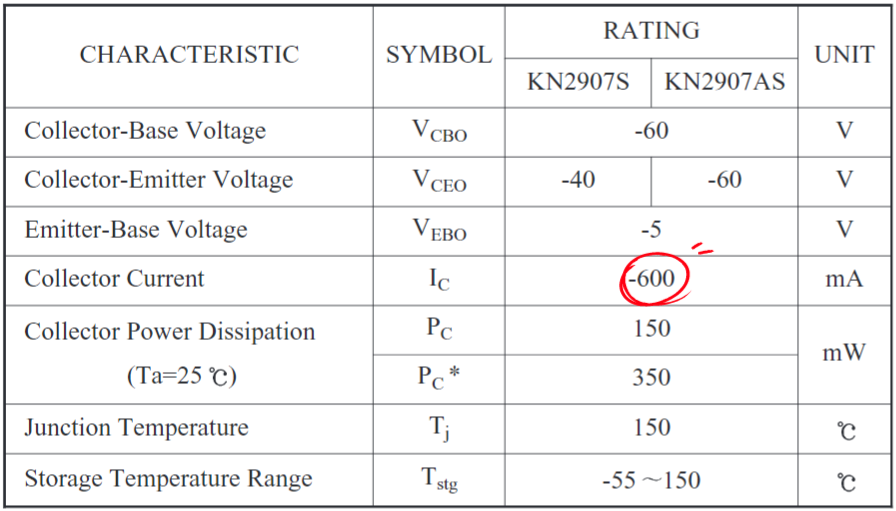

| PSpice for TI - Simulation(Transistor) (0) | 2025.03.16 |

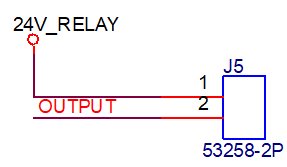

| 전자 회로 설계 - Relay, SSR 사용과 회로 설계 (0) | 2025.03.16 |

| 전자 회로 설계 - [I/O] PUSH-PULL, OPEN-DRAIN (0) | 2025.03.16 |